Projekt polegał na zaprojektowaniu stopera/minutnika/zegara przy użyciu programowalnego układu cyfrowego FPGA. Wykorzystane zostało rozbudowane oprogramowanie Xilinx ISE oraz ModelSIM, całość opisana jest w języku VHDL.

Projekt realizowany był w kooperacji z Jackiem Symonowiczem.

Sprawozdanie

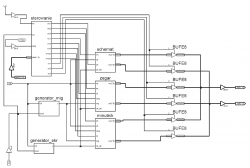

"Celem projektu było zaprogramowanie układu Spartan-II tak, aby spełniał funkcję stopera. Do dyspozycji był zestaw szkoleniowy wyposażony w układ Spartan-II, wyświetlacz dynamiczny LED (zespół wyświetlaczy siedmiosegmentowych), 4 przełączniki (typu dip switch) oraz jeden swobodny przycisk (button). Te same wyprowadzenia, które podłączone są do zespołu wyświetlaczy, są podłączone również do dwóch pojedynczych wyświetlaczy siedmiosegmentowych, nie mogą być więc równocześnie używane. Postanowiono wykorzystać maksymalnie możliwości zestawu, dlatego dodano jeszcze funkcje ustawialnego zegara czasu rzeczywistego oraz minutnika. (...)

"Celem projektu było zaprogramowanie układu Spartan-II tak, aby spełniał funkcję stopera. Do dyspozycji był zestaw szkoleniowy wyposażony w układ Spartan-II, wyświetlacz dynamiczny LED (zespół wyświetlaczy siedmiosegmentowych), 4 przełączniki (typu dip switch) oraz jeden swobodny przycisk (button). Te same wyprowadzenia, które podłączone są do zespołu wyświetlaczy, są podłączone również do dwóch pojedynczych wyświetlaczy siedmiosegmentowych, nie mogą być więc równocześnie używane. Postanowiono wykorzystać maksymalnie możliwości zestawu, dlatego dodano jeszcze funkcje ustawialnego zegara czasu rzeczywistego oraz minutnika. (...)

Z całą pewnością można było zaprojektować i zrealizować układ o podobnej funkcjonalności w postaci bardziej zintegrowanej, ale ważniejsze dla nas była budowa modularna i niezależność poszczególnych modułów. Takie podejście daje później możliwość łatwiejszego wprowadzania modyfikacji do projektu, czy wymiany danego modułu na inną jego wersję bez ingerencji w pozostałe. Układ w postaci, w jakiej został zaprojektowany, zsyntezowany i przetestowany, jest poprawnie działającą implementacją stopera, minutnika oraz zegara czasu rzeczywistego w jednym. Założenia projektowe zostały więc w pełni zrealizowane."